2 INTEL 64 AND IA-32 PROCESSOR ARCHITECTURES¶

本文更新于 2018.10.26

Skylake Server¶

Skylake¶

Haswell¶

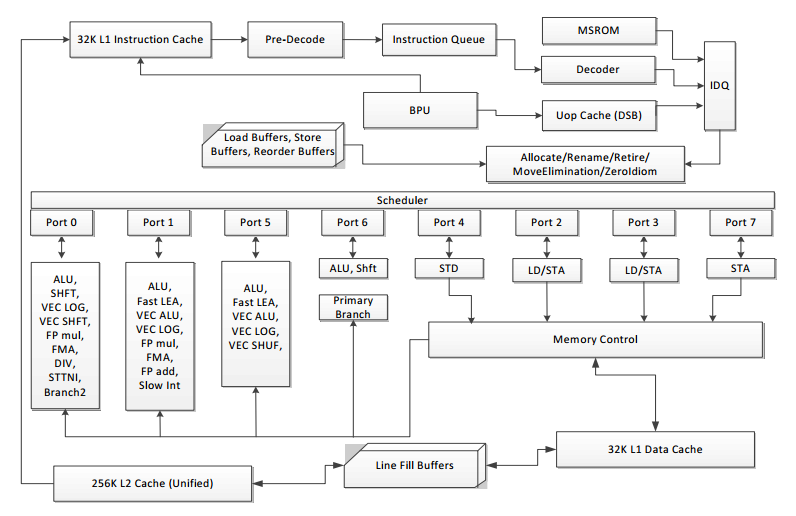

Haswell微架构构建在Sandy Bridge与Ivy Bridge微架构的成功之上。Haswell微架构的基本流水线功能描述在图2-2中。总之,在2.2.1-2.2.4节描述的大多数特性也适用于Broadwell微架构。Broadwell微架构的增强汇总在2.2.6节。

Haswell微架构的CPU核心流水线功能

Haswell微架构提供了以下创新的特性:

- 支持Intel先进向量扩展2(Intel Advanced Vector Extensions 2,Intel AVX2),FMA

- 支持加速整数值加密(integer numericencrytion)的通用的新指令

- 支持Intel®事务式同步的扩展(Intel® Transactional Synchronization Extensions,Intel® TSX)

- 每核每周期可以分发多达8个微操作

- 用于内存操作,FMA,AVX浮点与AVX2整数执行单元的256比特数据通路

- 提升L1D与L2缓存带宽

- 两条FMA执行流水线

- 四个算术逻辑单元(ALU)

- 三个写地址端口

- 两个分支执行单元

- 用于IA处理器核与非计算内核子系统的先进电源管理特性

- 支持可选的第四级缓存

Haswell-E¶

基于Haswell-E微架构的Intel处理器,如在Haswell微架构中描述的那样,由相同的处理器核组成,但提供更先进的非计算内核与集成I/O功能。基于Haswell-E微架构的处理器支持有多个插槽的平台。

Haswell-E微架构支持用于可扩展与高性能的多用途处理器架构及平台配置。由Haswell-E微架构的非计算内核及集成I/O子系统提供的某些功能包括:

- 在多插槽配置中支持多个Intel QPI内联。

- 每个物理处理器多达两个集成内存控制器。

- 每个物理处理器多达40路PCIExpress* 3.0连接。

- 每个物理处理器中多达18个处理器核通过两个环互联到L3。

Broadwell¶

Intel Core M处理器基于Broadwell微架构。Broadwell微架构构建在Haswell微架构的基础上, 并提供几处增强。本节描述Broadwell微架构的增强特性。

- 浮点乘法指令时延从前代的5个周期降到3个周期。这适用于AVX,SSE与FP指令集。

- Gather指令的吞吐率显著提高,参考表C-5。

- 在Broadwell微架构里PCLMULQDQ指令实现是改进了时延与吞吐率的单个微操作。

TLB层次结构包含指令缓存专用的第一级TLB,用于L1D的TLB,加上用于L2的一体化TLB。